General Recommendations:

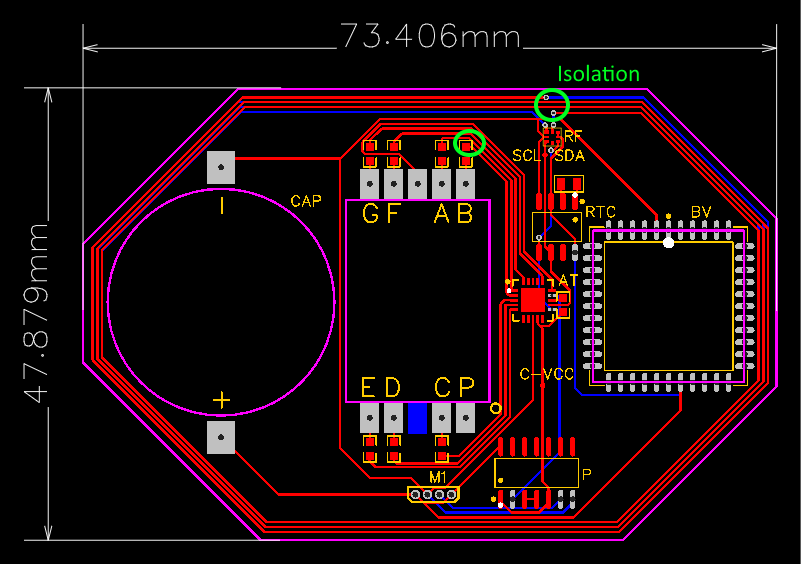

Be careful to make sure there is enough isolation between traces that carry different signals. Usually a design rules check will catch these, but the DRC needs to be set up correctly for your fabricator and you have to not override them. I would also add two Through-hole pins for external power and ground to aid your testing. You may also want SMD footprints connecting the SDA and SCL traces to power as pull-ups, Just in case it’s difficult to set internal pull-ups on the ATTiny.

Your Questions:

The vias for the antenna are a bit close to the antenna traces, there might be shorts. You always have to plan for manufacturing tolerances. Via-in-pad is generally acceptable, but it does require an extra processing step during fabrication. Often for the lowest cost PCB deals the fabricator will flag designs with via-in-pad and say you can’t do that. Otherwise you need to message them back several times in the middle of the night and fight it, or just pay more.

For test boards I would always make the board way bigger than you need to give you room to work with and troubleshoot, then you can miniaturize in another revision. Since none of these will be implanted yet don’t make your life more difficult (and expensive) than it needs to be. Personally I would make the board outline larger and make the two ends half-circles. You can usually make two arcs with radii that are half the width of the board to create half-circles. Countersinking usually means carving a 3-dimensional divet in the substrate to allow parts to sit flush. In this case the design is only 2.5-dimensional so you would just be making holes. I don’t think it’s necessary in this case, just make it a solid board with the parts sitting on top.

A ground plane would block the flux in the center of the antenna and also add parasitics that would throw off the tuning. Almost universally I add a ground plane for normal boards, but never add one for RFID boards.

I can calculate the antenna dimensions for you using this calculator I published. It’s not perfect, but it will get you very close. You can get even closer if we undershoot the inductance for the antenna and you add a footprint for an SMD capacitor in parallel with the antenna pads on the NFC chip. If you want more information on this process you can check out this thread. I’ll get back to you on that in a few minutes.

I think the plan is to use the NTAG I2C Plus to communicate with the ATTiny and set new time values that it will then relay to the RTC. In the original Endochron design concept we planned to use an NTAG 5 with a transparent I2C master channel to skip the MCU entirely, but this will do for now since it will be easier to set up for testing.